Witness the recent announcements by a number of EDA companies – Altium, Synopsys, and others – touting team design enhancements in their tools. With their latest ISE release – ISE 13.1 – Xilinx is joining that group with a major set of improvements for multi-engineer FPGA projects.

Team design has been around for a long time, of course. Since the beginning of engineering, engineers have been collaborating on large projects. But FPGAs have still often been one-man shows, where the FPGA part of the large project was primarily the job of one member of the team. Now, however, with the advent of large systems-on-FPGA, more of the design project is taking place inside the FPGA, and less elsewhere. Other engineers are squeezing into the FPGA part of the project, and it’s getting a little crowded in there.

Now, for example, the FPGA often has an embedded processor (or several) inside – which means there are embedded engineers and software/firmware people poking around in there. It is also doing DSP acceleration – so those guys are hanging out with their Matlab models, trying to work their way into the FPGA code. There is also just a massive amount of pure logic available in the latest FPGAs – up to a staggering 2 million LUT4 equivalents in Xilinx’s upcoming Virtex-7 family. All that logic takes more engineering to fill, of course. These forces are all combining to drive the current push for team design support.

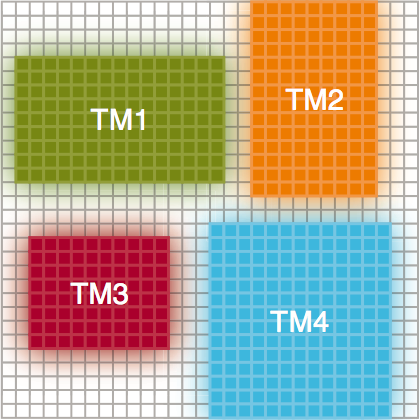

Xilinx’s big change in ISE comes from a small company – one they acquired about seven years ago. Hier Design was a San Jose-based startup that had the novel idea that ASIC-grade floorplanning would be a valuable technology for FPGA design. They were about half a decade ahead of the market with that, and they were acquired by Xilinx when the floorplanning market failed to materialize. The resulting technology, PlanAhead, has been floating around in the Xilinx tool offering ever since – gradually gaining importance and capability. Now, PlanAhead is front and center in the newly team-friendly ISE 13.1.

PlanAhead today bears little resemblance to what left Hier Design all those years ago. While floorplanning technology is still hard at work down inside there somewhere, the capabilities have been expanded to cover a whole range of FPGA design- and project-planning capabilities, as well as control of the overall tool flow, via a new feature called the “Flow Navigator.” The Flow Navigator guides us through the design process from RTL design down through device programming and debug – including project management capabilities. In the new PlanAhead, Xilinx has created a “layered complexity” user interface that seeks to make the design process easy and approachable for new users, but with additional capabilities disclosed to support advanced users. Part of the nod to advanced users, of course, is a full-fledged scripting interface that allows everything to be done outside the GUI as well.

Also inside PlanAhead, Xilinx has boosted the capabilities of their power estimator, improved visibility of clocking resources, and integrated the native ISE simulator – iSim (not an Apple product). This is the most aggressive positioning we’ve seen of Xilinx’s own simulation technology versus third-party simulators and OEM versions. In addition to more prominent integration in the ISE user interface, Xilinx has added compelling capabilities like hardware co-simulation, which allows blocks to be moved into the FPGA fabric on your development board, and for that hardware implementation to be used inside the software simulation of your design for “up to 100 times” simulation acceleration. For people doing designs with high-performance datapaths, for example, this capability could come in very handy in debug.

Another issue with complex collaborative design is IP sharing and re-use, and third-party IP integration. ISE 13.1 continues the push to make IP more plug-and-play, including more support for AXI4 IP, IP-XACT repositories, a bunch of new domain-specific IP blocks in areas like audio, video, and image processing; communications and DSP; wireless, and more. There is also an automatic IP upgrade flow.

As FPGAs spread into more diverse application areas and simultaneously take charge of more responsibility in each design, we will continue to see a need for more plug-and-play IP, more special-purpose IP libraries for specific application areas, and more third-party IP created by specialty houses with expertise in a particular design area. Xilinx seems to be laying the groundwork for all of these with the continual ramp-up of support in ISE.

In addition to the improvements in team design, simulation performance, and IP re-use, there are a number of improvements in embedded design, DSP support, and, of course, support for the upcoming 7-series devices. There is also improved support for partial reconfiguration, making these gigantic FPGAs act like even more gigantic ones. While the devices themselves won’t be available for a while, it is certainly not too early to begin doing design work to see how they’ll work for your long-range projects. If you’re trying to fill up a 2 million LUT FPGA with something interesting, your design won’t be done overnight.

One thing that doesn’t get much attention in new tool rollouts is continued improvement in the basics of FPGA design. However, Xilinx claims significant runtime and quality-of-results improvements in this version of ISE. It may seem surprising that a large body of software would still have potential for major performance improvements after decades of tuning by a large team of engineers. However, the complexity of design software is such that there are always data structures that can be optimized, memory operations that can be improved, and algorithms that can be replaced – with significant payoffs in performance. (Or, the engineers may be just cleverly taking out a few “wait” statements and empty “for” loops with each new version just to keep themselves employed.) It’s a good thing, too. Simple Moore’s Law improvements in computer power have not kept up with the increasing size and complexity of programmable logic devices in recent years, so if we didn’t get some serious speed-ups from the tool developers, we wouldn’t be able to get our work done in a reasonable amount of time.

Even with the new team-design features in the ISE, the roadmap is obviously far from complete. Xilinx’s team-design support doesn’t include the complex design-repository, check-in/check-out, design configuration, release management, ECO handling, and other major collaboration features one could imagine. It also doesn’t offer significantly better support for teams that are non-co-located – working on the same project on different continents in different time zones. Perhaps these needs would be best served by a cloud-based tool infrastructure in the future. In addition, ISE is also still a collection of point tools flying in tight formation, rather than a fully-integrated seamless set of capabilities operating on one data model. However, there are rumors that a more comprehensive overhaul may be in the works, so stay tuned.

In the meanwhile, ISE 13.1 looks like a significant improvement over previous editions, so jump on in and design some stuff, then drop us a note and tell us about it.